- High Pressure (500-10k psi)

- Media Isolated -SS316

- -20-125°C (150C Avail) Operating Temperature

- · Compact Size

- 5 ms Response Time

- · 1% Total Error Band

- Digital Output SPI, I2C

- Low-Power (<5uA Stand-by)

- Media Harsh Liquid, Air, & Gas

#### **DESCRIPTION**

The PPT82 is a digital (I2C, SPI) pressure transducer manufactured for a high operating temperature range for the most challenging of applications. This silicon pressure transducer was designed for industrial and commercial applications. The stainless steel design and high temperature analog component selection allows the sensor to be used in high temperature applications.

The PPT82 series utilizes MEMS piezo-resistive sensors pressurized on the passive backside of the SS housing which has superior long term stability and accuracy (.25% Linearity).

The design is simple, cost effective, and proves reliable for OEM customers. Please contact us for Custom design availability.

#### **APPLICATIONS**

- Mil/Aero

- Industrial Automation

- HVAC

- Automotive Engine

- Compressor

- Pneumatic

## Maximum Environmental Ratings

Operating Temperature ......-20°C to 125°C Proof pressure Storage Temperature Range .....-55°C to 130°C Burst pressure pressure Proof pressure pres

## **Application Information**

#### **Package**

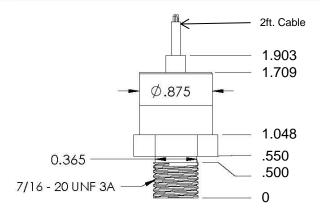

The one piece body design is made of stainless steel (SS316L), which allows for easy manufacturability and long term stability. Automotive grade vibration proof design for engine mount.

#### **Stability**

The silicon MEMS pressure sensor element is media isolated and hermetically sealed into the SS housing. The selection of thermally capability materials reduce the mechanical stress on the sensor resulting in greater stability over time and temperature.

Additional stability is gained from factory stabilization of all sensors.

#### **Pressure port**

1/4" -18NPT and 1/8"-18NPT threads are standard SS fittings. Other port fittings such as 7/16-20UNF, and 1/4" BSP are available for OEM customers.

#### Media

The pressure port is tolerant to most media including but not limited to oil, air, gas, some corrosive media, and salt water.

#### Wetted parts

When checking media capability, the wetted surface is composed of only stainless steel (316).

#### Pressure ranges

Standard pressure ranges are 500, 1000, 1500, 200, and 3000 psi in absolute and gage. Custom pressure ranges are available for OEM customers.

# PPT82 Digital Output Operational Characteristics

| $V_{+} = 5V$ , $V_{-} = 0V$ , Temperature  | = 25°C           |       |              |      |             |

|--------------------------------------------|------------------|-------|--------------|------|-------------|

| PARAMETER                                  | SYMBOL           | Min   | Тур          | Max  | UNITS       |

| Supply Voltage                             | V <sub>DD</sub>  | 2.7   | 5            | 15   | V           |

| Operating Temperature                      | Ts               | -20   |              | 125  | С           |

| Supply Current (Note 1)                    | l <sub>DD</sub>  | 70    | 120          | 2500 | μА          |

| Sleep Mode Supply<br>Current               | stdby            |       | .5           | 32   | μΑ          |

|                                            |                  | А     | ccuracy      |      |             |

| Total Error Band                           |                  | 5     |              | .5   | %Full Scan  |

| Non-Linearity (Note 2)                     |                  | 1     |              | .1   | %Full Scan  |

| Temperature Error (Null and Span) (Note 3) |                  | -1    | .5           | 1    | С           |

| Response Time                              | t <sub>R</sub>   | 1     | 2            | 20   | ms          |

|                                            |                  | Analo | g-to-Digital |      |             |

| Resolution                                 | ADC              |       | .004         |      | %Full Scale |

| Temperature<br>Resolution                  |                  |       | .05          |      | %Full Scale |

| I2C & SPI Interface                        |                  |       |              |      |             |

| Input Low Level                            | Vin_low          | 0     |              | .2   | Vdd%        |

| Input High Level                           | <b>V</b> in_high | .8    |              | 1    | Vdd%        |

| Output Low Level                           | Vo_low           |       |              | .1   | Vdd%        |

| Load Capacitance @SDA                      | Csda<br>@400khz  |       |              | 200  | pF          |

| Pull-Up Resistor                           | RI2C_PU          | 500   |              |      | Ω           |

| Input Capacitance (each pin)               | Cl2C_ln          |       |              | 10   | pF          |

Notes: 1) Measured at zero pressure. 2) Defined as best straight line 3) Measured from  $0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ .

# Electrical Pin Configuration (Digital [SPI, I2C])

Fig. 2

Orange - SCL/SCLK Yellow - SDA/MISO Green- INT/SS Red- V+In Black GND

## Digital Output (SPI, I2C) Communication

#### 2.3. Digital Signal Processor

A digital signal processor (DSP) is used for processing the converted differential signal as well as performing temperature correction and computing the temperature value for digital output.

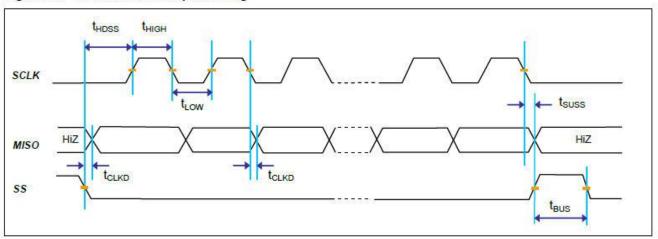

#### 2.3.2. Normal Operation Mode

Two operation modes are available for normal operation: Update Rate Mode (continuous conversion at a select-able update rate) or Sleep Mode (low power). (See section 3.1.) Both modes can operate in either I2C digital out-put or SPI digital output. These selections are made at the factory. Factory Default is SPI.

#### 2.3.3. **EEPROM**

The EEPROM array contains the calibration coefficients for gain and offset, etc., and the configuration bits, such as output mode, update rate, etc.

IMPORTANT: The EEPROM is locked at factory.

#### 2.3.4. Digital Interface - I2C

The IC can communicate via an addressable two-wire (I2C) interface. Commands are available for the following:

Starting measurements in Sleep Mode

Reading data

The PPT82 uses an I2C-compatible communication protocol with support for the bit rates listed in Table 2.7.

#### Table 2.7 Supported I2CTM Bit Rates Clock Setting Bit Rates (FACTORY Set at 4MHz)

4MHz 400kHz or 100kHz

1MHz 100kHz

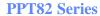

See below- Figure 2.6 for the I2C timing diagram and Table 2.8 for definitions of the parameters shown in the timing diagram.

Table 2.8 I<sup>2</sup>C™ Parameters

| PARAMETER                                                | SYMBOL             | MIN | TYP | MAX | UNITS |

|----------------------------------------------------------|--------------------|-----|-----|-----|-------|

| SCL clock frequency                                      | f <sub>SCL</sub>   | 100 |     | 400 | kHz   |

| Start condition hold time relative to SCL edge           | t <sub>HDSTA</sub> | 0.1 |     | 8.  | μs    |

| Minimum SCL clock low width <sup>1</sup>                 | t <sub>LOW</sub>   | 0.6 |     |     | μs    |

| Minimum SCL clock high width <sup>1</sup>                | t <sub>HIGH</sub>  | 0.6 |     |     | μS    |

| Start condition setup time relative to SCL edge          | t <sub>susta</sub> | 0.1 |     |     | μs    |

| Data hold time on SDA relative to SCL edge               | t <sub>HDDAT</sub> | 0   |     |     | μs    |

| Data setup time on SDA relative to SCL edge              | tsudat             | 0.1 |     |     | μS    |

| Stop condition setup time on SCL                         | t <sub>susto</sub> | 0.1 |     |     | μs    |

| Bus free time between stop condition and start condition | t <sub>BUS</sub>   | 2   |     |     | μs    |

<sup>&</sup>lt;sup>1</sup> Combined low and high widths must equal or exceed minimum SCL period.

Figure 2.6 I<sup>2</sup>C™ Timing Diagram

(See section 3.1 for data transmission details.)

### Note: There are three differences in the PPT82 protocol when compared to standard I2C protocol:

- •Sending a start-stop condition without any transitions on the CLK line (no clock pulses in between) creates a communication error for the next communication, even if the next start condition is correct and the clock pulse is applied. An additional start condition must be sent, which results in restoration of proper communication.

- •The restart condition—a falling SDA edge during data transmission when the CLK clock line is still high—creates the same situation. The next communication fails, and an additional start condition must be sent for correct communication.

- •A falling SDA edge is not allowed between the start condition and the first rising SCL edge. If using an I2C address with the first bit 0, SDA must be held low from the start condition through the first bit.

### SPI – Digital Interface

### 2.3.5. Digital Interface - SPI

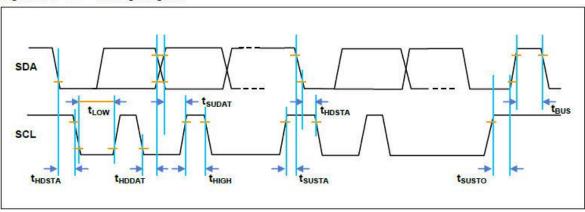

SPI is available only as half duplex (read-only from the PPT82). SPI cannot be used in the calibration environment (Command Mode) because it does not support receiving commands. SPI speeds of up to 800kHz can be supported in 4MHz Mode (200kHz in 1MHz Mode). See Figure 2.7 for the SPI timing diagram and Table 2.9 for definitions of the parameters shown in the timing diagram.

Table 2.9 SPI Parameters

| PARAMETER                                 | SYMBOL            | MIN | TYP | MAX | UNITS |

|-------------------------------------------|-------------------|-----|-----|-----|-------|

| SCLK clock frequency (4MHz clock)         | f <sub>SCL</sub>  | 50  |     | 800 | kHz   |

| SCLK clock frequency (1MHz clock)         | f <sub>SCL</sub>  | 50  |     | 200 | kHz   |

| SS drop to first clock edge               | t <sub>HDSS</sub> | 2.5 |     |     | μS    |

| Minimum SCLK clock low width              | t <sub>LOW</sub>  | 0.6 |     |     | μs¹   |

| Minimum SCLK clock high width             | t <sub>HIGH</sub> | 0.6 |     |     | μs¹   |

| Clock edge to data transition             | t <sub>CLKD</sub> | 0   |     | 0.1 | μS    |

| Rise of SS relative to last clock edge    | t <sub>suss</sub> | 0.1 |     |     | μS    |

| Bus free time between rise and fall of SS | t <sub>BUS</sub>  | 2   |     |     | μs    |

<sup>&</sup>lt;sup>1</sup> Combined low and high widths must equal or exceed minimum SCLK period.

Figure 2.7 SPI Bus Data Output Timing

(See section 3.1 for data transmission details.)

### 2.3.6. Clock Generator / Power-On Reset (CLKPOR)

The PPT82 has an internal 4MHz temperature compensated oscillator that provides the time base for all operations. This oscillator feeds into a 4:1 post scalar that can optionally form the clock source for the device. The FACTORY default setting is 4MHz clock digital core clock for the PPT82. If the fast response times and sampling periods provided by the 4MHz clock are not required by the customer, then the FACTORY can select the 1MHz clock which will result in better overall resolution performance.

If the power supply exceeds  $\approx$ 1.9V, the reset signal de-asserts and the clock generator starts working at the selected frequency (approximately 1MHz or 4MHz). The exact value only influences the conversion cycle time. To minimize the oscillator error as the VDD voltage changes, an on-chip regulator supplies the oscillator block.

### Functional Description

#### 3.1. General Working Mode

See Figure 3.1 for an overview of the general working mode of the PPT82. There are three types of commands as detailed in Table 3.1.

Table 3.1 Command Types

| Туре                        | Description                                 | Communication<br>Supported | Reference Sections                  |

|-----------------------------|---------------------------------------------|----------------------------|-------------------------------------|

| Data Fetch (DF)             | Used to fetch data in any mode              | I <sup>2</sup> C and SPI   | Sections 3.2.2<br>and 3.3.2         |

| Measurement<br>Request (MR) | Used to start measurements in<br>Sleep Mode | I <sup>2</sup> C and SPI   | Sections 3.1.2,<br>3.3.1, and 3.4.1 |

Sensor will start performing the required A2D conversions 10 milliseconds after power up. DO NOT ISSUE ANY COMMAND DURING THIS START UP TIME. The first corrected data will be written to the digital interface within 6ms of power-on with a 4MHz clock and the EEPROM locked.

Operation after the power-on sequence depends on whether the part is programmed in Sleep Mode or in Update Mode. The factory will set up part in Sleep Mode or Update mode. In Sleep Mode, the part waits for commands from the master before taking measurements. In Update Mode, data is taken at a fixed, selectable rate. More detail is given about Update Mode and Sleep Mode in sections 3.1.1 and 3.1.2 respectively.

### **Functional Description**

#### 3.1.1. Update Mode

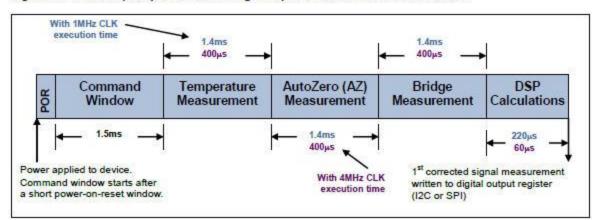

In Update Mode, the digital core will perform measurements and correction calculations at a selectable update rate and update the I2C/SPI output register. The power-on measurement sequence for the Update Mode is shown in Figure 3.2.

Figure 3.2 Power-Up Sequence and Timing for Update Mode with EEPROM Locked "

\*\* When EEPROM is not locked, the command window is 4.5ms longer (= 6ms). All time values shown are typical; for the worst

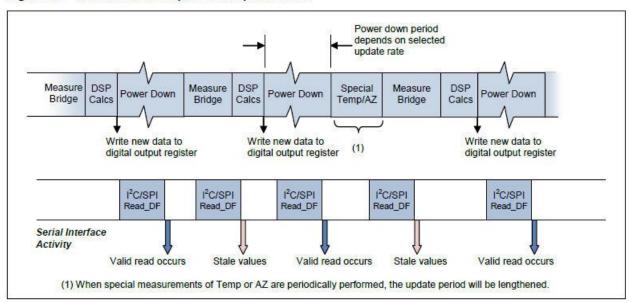

If the part is programmed for the fastest update rate, conversions will continue to happen after the power-up sequence. If the PPT82 is not in the fastest update rate, the part will power down after writing to the digital output register. The duration of the power-down period is determined by the Update Rate setting (bits [7:6] in EEPROM word 01HEX; see section 3.6) and the digital core clock speed (see section 2.3.6). See Table 3.2 and Table 3.3 for the update rates. After the power-down period has expired, the PPT82 will power up; take another bridge reading followed by calculations; write to the digital output register; and power down. Temperature and Auto-Zero (AZ) are slower moving quantities but must be updated periodically. When the part is configured in Update Mode, these two quantities are measured periodically (referred to as special measurements).

As illustrated in Figure 3.3, valid data output to the digital register occurs after the measurement and the DSP calculations are complete. At this point the master can fetch the data in I2C or SPI with a Read\_DF command. Specifics of the Read\_DF command are given in sections 3.2 and 3.3. After a valid output has been read by the master, the status bits are set to "stale," indicating that the measurement has not been updated since the last Read\_DF. This mode allows the application to simply read the digital output at any time and be assured the data is no older than the selected update period. See Table 2.10 for more information on the status bits. The chip should be polled at a frequency slower than 20% more of the update rate period listed in Table 3.2 and Table 3.3.

In I2C Mode only, the INT/SS pin will assume the INT (interrupt) function. Instead of polling until a "valid" response is received, the application can look for a rise on the INT pin. This will indicate that the measurement and calculations are complete and new valid data is ready to be read on the I2C interface.

Table 3.2 Update Rate Settings (Normal Integration Mode: 9 Coarse + 5 Fine) 1

| Update_Rate     | Update Period/1MHz<br>Clock | Update Period/4MHz<br>Clock | Measurement Cycles between<br>Special Measurements<br>(Temperature or AZ) |

|-----------------|-----------------------------|-----------------------------|---------------------------------------------------------------------------|

| 00 <sup>2</sup> | 1.6ms                       | 0.5ms                       | 255                                                                       |

| 01              | 5.0ms                       | 1.5ms                       | 127                                                                       |

| 10              | 25.0 ms                     | 6.5ms                       | 31                                                                        |

| 11              | 125.0ms                     | 32.0ms                      | 15                                                                        |

<sup>&</sup>lt;sup>1</sup> All time values shown are typical; for worst case values, multiply by 1.15 (nominal frequency ±15%).

Factory setting will be Update\_Rate 00 with an update period of .5ms. This value can be adjust by request.

Figure 3.3 Measurement Sequence in Update Mode

The benefit of slower update rates is power savings. If the update period is increased, the device will be powered down for longer periods of time, so power consumption will be reduced. When a special measurement occurs, a BP/BN (bridge) measurement will occur directly afterward. The update period during this special measurement will be increased by one conversion time over the standard measurement period.

<sup>&</sup>lt;sup>2</sup>With the fastest update rate setting, there is no power down period between measurements.

### Sleep Mode

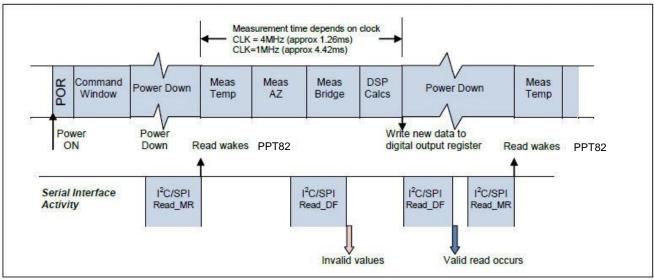

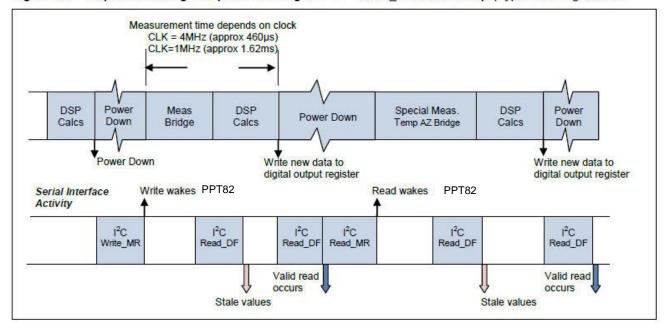

In Sleep Mode, after the command window, the PPT82 will power down until the master sends a Read\_MR (either I2C or SPI) or a Write\_MR (I2C only). Specifics on the Read\_MR and Write\_MR commands are given in sections 3.2.1, 3.3.1, and 3.4.1. A Read\_MR or Write\_MR wakes the PPT82and starts a measurement cycle. If the command is Read\_MR, the part performs temperature, auto-zero (AZ), and a bridge measurement followed by the DSP correction calculations (see Figure 3.4). If the command is Write\_MR, the part measures only the bridge and performs the correction calculations using previously measured temperature and auto-zero data (see Figure 3.5). Valid values are then written to the digital output register, and the PPT82 powers down again.

Following a measurement sequence and before the next measurement can be performed, the master must send a Read\_DF command, which will fetch the data as 2, 3 or 4 bytes (see section 3.2.2), without waking the PPT82. When a Read\_DF is performed, the data packet returned will be the last measurement made with the status bits set to "valid." See Table 2.10 for more information on the status bits. After the Read\_DF is completed, the status bits will be set to "stale." The next Read\_MR or Write\_MR will wake the part again and start a new measurement cycle. If a Read\_DF is sent while the measurement cycle is still in progress, then the status bits of the packet will read as "stale." The chip should be polled at a frequency slower than 20% more than the Sleep Mode response times listed in Table 3.4 and Table 3.5.

Table 3.4 Sleep Mode Response Times (Normal Integration Mode: 9 Coarse + 5 Fine) 1

| Measurement Request | Response/1MHz Clock | Response/4MHz Clock |  |

|---------------------|---------------------|---------------------|--|

| Read MR             | 4.5ms               | 1.5ms               |  |

| Write MR            | 1.5 ms              | 0.5ms               |  |

All time values shown are typical; for worst case values, multiply by 1.15 (nominal frequency ±15%).

Table 3.5 Sleep Mode Response Times (Long Integration Mode: 10 Coarse + 5 Fine) 1

| Measurement Request | Response/1MHz Clock | Response/4MHz Clock |

|---------------------|---------------------|---------------------|

| Read MR             | 12ms                | 4.5ms               |

| Write MR            | 5.5 ms              | 1.5ms               |

<sup>&</sup>lt;sup>1</sup> All time values shown are typical; for worst case values, multiply by 1.15 (nominal frequency ±15%).

**Note:** Data is considered invalid from system power-on reset (POR) until the first measured data is written to the digital register. Sending an I2C Write\_MR as the first command after power-on delivers invalid data; even though the status bits report it as "valid". This is due to the correction calculations being performed with an uninitialized temperature and Auto-Zero value.

In I2C Mode only, the INT/SS pin will assume the INT (interrupt) function. Instead of polling until a "valid" response is received, the application can look for a rise on the INT pin. This will indicate that the measurement and calculations are complete, and new valid data is ready to be read on the I2C interface.

Figure 3.4 Power-on Sequence in Sleep Mode for I<sup>2</sup>C™ or SPI Read\_MR (Typical Timing Values<sup>††</sup>)

Figure 3.5 Sequence during Sleep Mode Using an I<sup>2</sup>C™ Write\_MR to Wake Up (Typical Timing Values<sup>††)</sup>

### Read Operations with I2C

### 3.2. PPT82 Read Operations with I2CTM

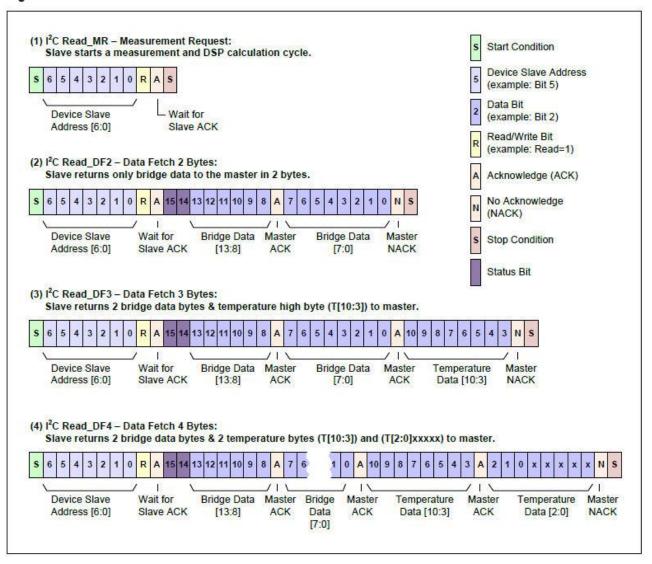

For read operations, the I2C<sup>™</sup> master command starts with the 7bit slave address with the 8th bit =1 (READ). The PPT82 as the slave sends an acknowledge (ACK) indicating success. The PPT82 has four I2C<sup>™</sup> read commands: Read\_MR, Read\_DF2, Read\_DF3, and Read\_DF4. Figure 3.6 shows the structure of the measurement packet for three of the four I2C<sup>™</sup> read commands, which are explained in sections 3.2.1 and 3.2.2.

Figure 3.6 I2C™ Measurement Packet Reads

#### 3.2.1. I2C<sup>TM</sup> Read\_MR (Measurement Request)

The Read\_MR (see example 1 in Figure 3.6) communication contains only the slave address and the READ bit (1) sent by the master. After the PPT82 responds with the slave ACK, the master must create a stop condition. This is only used in Sleep Mode (see section 3.1.2) to wake up the device and start a complete measurement cycle (including the special measurements) followed by the DSP calculations and writing the results to the digital output register.

Note: The I2C™ Read\_MR function can also be accomplished using the I2C™ Read\_DF2 or Read\_DF3 command and ignoring the "stale" data that will be returned.

#### 3.2.2. I2C<sup>TM</sup> Read DF (Data Fetch)

For Data Fetch commands, the number of data bytes returned by the PPT82 is determined by when the master sends the NACK and stop condition. For the Read\_DF3 data fetch command (Data Fetch 3 Bytes; see example 3 in Figure 3.6), the PPT82 returns three bytes in response to the master sending the slave address and the READ bit (1): two bytes of bridge data with the two status bits as the MSBs and then 1 byte of temperature data (8-bit accuracy). After receiving the required number of data bytes, the master sends the NACK and stop condition to terminate the read operation.

For the Read\_DF4 command, the master delays sending the NACK and continues reading an additional final byte to acquire the full corrected 11-bit temperature measurement. In this case, the last 5 bits of the final byte of the packet are undetermined and should be masked off in the application.

The Read\_DF2 command is used if corrected temperature is not required. The master terminates the READ operation after the two bytes of bridge data (see example 2 in Figure 3.6).

#### 3.3. SPI Read Operations

The SPI interface of PPT82 can be programmed for falling-edge MISO change or rising-edge MISO change (see SPI\_Polarity, bit 0 of EEPROM word 02HEX, in section 3.6). **Falling-edge is the factory default.**

#### 3.3.1. SPI Read MR (Measurement Request)

A special SPI Read\_MR command is used for waking up the part in Sleep Mode (see section 3.1.2). It performs a measurement cycle including the special measurements and a correction calculation. The SPI Read\_MR command only requires that the SS line be dropped low for a minimum of  $8\mu$ s then raised high again. The rise of SS will trigger the part to power up and perform the measurements.

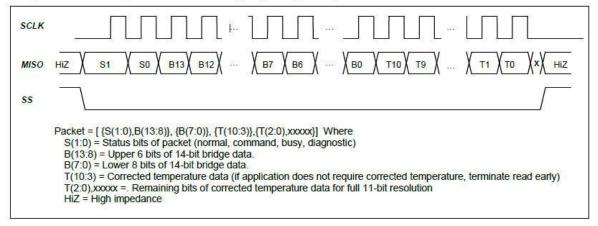

#### 3.3.2. SPI Read DF (Data Fetch)

For simplifying explanations and illustrations, only falling edge SPI polarity will be discussed in the following sections. The SPI interface will have data change after the falling edge of SCLK. The master should sample MISO on the rise of SCLK. The entire output packet is 4 bytes (32 bits). The high bridge data byte comes first, followed by the low bridge data byte. Then 11 bits of corrected temperature (T[10:0]) are sent: first the T[10:3] byte and then the {T[2:0],xxxxx} byte. The last 5 bits of the final byte are undetermined and should be masked off in the application. If the user only requires the corrected bridge value, the read can be terminated after the 2nd byte. If the corrected temperature is also required but only at an 8-bit resolution, the read can be terminated after the 3rd byte is read.

Figure 3.8 SPI Output Packet with Falling Edge SPI\_Polarity

### **I2C Write Operations**

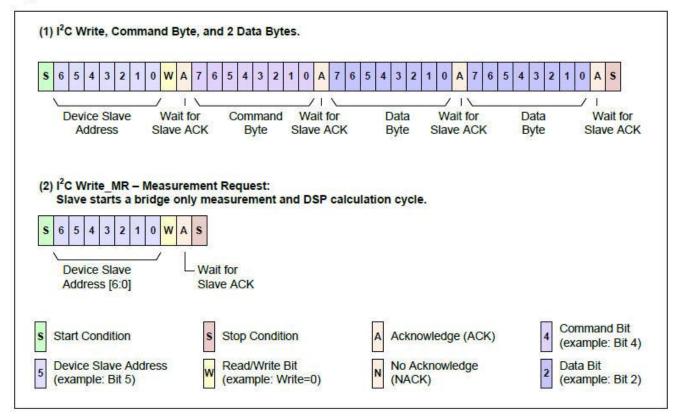

#### 3.4. I2CTM Write Operations

For write operations, the I2C<sup>TM</sup> master command starts with the 7-bit slave address with the 8th bit =0 (WRITE). The PPT82 as the slave sends an acknowledge (ACK) indicating success. The PPT82 has two general I2C<sup>TM</sup> write command formats: I2C<sup>TM</sup> WRITE and I2C<sup>TM</sup> Write\_MR. Figure 3.9 shows the structure of the write packet for the two I2C<sup>TM</sup> write commands, which are explained in sections 3.4.1 and 3.4.2.

Figure 3.9 I<sup>2</sup>C™ Measurement Packet Writes

#### 3.4.1. I2C<sup>TM</sup> Write MR (Measurement Request)

Write\_MR is a special I2C<sup>TM</sup> write operation, which only includes the 7-bit slave address and the WRITE bit (0). This command can only be sent in Sleep Mode (see section 3.1.2). It wakes up the part and starts a measurement cycle for the bridge values only (no special measurement) and a DSP calculation based on former AZ and Temperature values. After finishing the calculation with valid results written to the digital register, the PPT82 powers down again and a Read\_DF (see section 3.2.2) is required to read the valid values. See Figure 3.9 for an illustration of Write\_MR.

Note: The I2C<sup>TM</sup> Write\_MR function can also be accomplished using the I2C<sup>TM</sup> WRITE command with "don't care" data in Sleep Mode.

### 3.4.2. Command Mode I2CTM Write Operations

With the exception of the I2C<sup>TM</sup> Write\_MR command, write operations typically only occur in Command Mode (see section 3.1) and are only supported for the I2C<sup>TM</sup> protocol. Command Mode write commands to the PPT82 are in 32-bit packets. After the write command byte (7-bit slave address followed by 0 for write), the next (2nd) byte is considered the command byte, and the subsequent two bytes form a 16-bit data field. See Figure 3.9 for an illustration of the Command Mode I2C<sup>TM</sup> WRITE command sequence.

Note: If data is not needed for the command, all zeros must be supplied as data to complete the 32-bit packet.

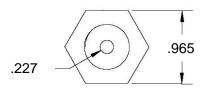

### Mechanical Dimensions (inches)

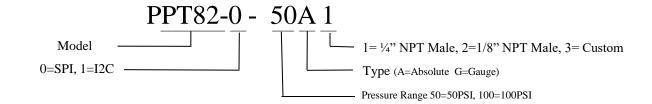

## Part Number Configuration

## **Standard Part Numbers**

| Model        | Pressure<br>Range<br>PSI | Туре     | Max<br>Over<br>Pressure |

|--------------|--------------------------|----------|-------------------------|

| PPT82-0-50A  | 50                       | Abs/Gage | 150                     |

| PPT82-0-100A | 100                      | Abs/Gage | 300                     |

| PPT82-0-300A | 300                      | Abs/Gage | 900                     |

Ph: (480) 462-1810 sales@PhoenixSensors.com

#### Notice:

Phoenix Sensors LLC reserves the right to make changes to the product contained in this publication. Phoenix Sensors LLC assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. While the information in this publication has been checked, no responsibility, however, is assumed for inaccuracies.

Phoenix Sensors LLC does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of a life-support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications.